Nellow invente les futures générations de puces

Créée en octobre 2024, la jeune start-up ambitionne de révolutionner l’industrie des semi-conducteurs en développant des puces à ultrabasse consommation énergétique.

Issue des laboratoires Spintec* et Albert Fert**, la toute récente société Nellow s'appuie sur une technologie de rupture qui combine ferroélectricité et matériaux quantiques, pour offrir des performances inégalées en termes d'efficacité énergétique. Contrairement aux architectures CMOS classiques, sa technologie intègre les fonctions logiques et la mémoire dans un seul composant, éliminant ainsi une grande partie du coût énergétique associé au transfert de données.

Basés sur une propriété physique, la ferroélectricité, les dispositifs logiques sont non volatils : ils conservent les données même sans être alimentés électriquement, ce qui réduit drastiquement la consommation d'énergie de la puce. En s'appuyant sur le transistor ferroélectrique spin-orbite, l’entreprise vise à dépasser les limites qui freinent aujourd'hui les gains de performance des puces classiques en raison de l’échauffement et de la dissipation thermique.

Des applications en IA

Nellow répond à un enjeu crucial, à l’heure où la loi de Moore atteint des limites, et où les besoins en calcul intensif explosent, notamment pour l’intelligence artificielle dont l’impact énergétique ne cesse de s’alourdir. La technologie de Nellow pourra réduire la consommation par opération de plusieurs ordres de grandeur par rapport aux standards actuels.

Lauréate du Concours i-Lab 2024 et soutenue par le programme Magellan du CEA, Nellow bénéficie d'un accompagnement stratégique pour accélérer le développement de ses prototypes. La start-up prévoit une levée de fonds de 10 M€ pour concrétiser ses objectifs, avec une première puce pour l'IA attendue en 2032. En s'inscrivant dans une démarche de souveraineté technologique, Nellow ambitionne de transformer le paysage de la microélectronique, tout en contribuant à un avenir plus durable.

* CEA, CNRS

** CNRS, Thales et Univ. Paris Saclay

L. Marty

Infos clés

Développement de composants à ultra-basse consommation d’énergie pour la logique et l’IA

Grenoble, avenue des Martyrs

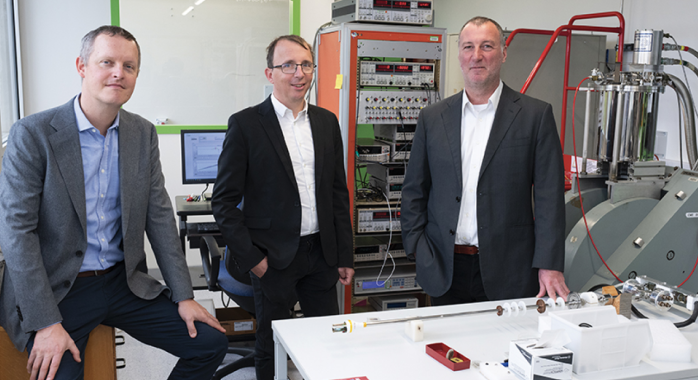

Trois fondateurs, Jean-Philippe Attané, Laurent Vila et Manuel Bibes

Embauche d’une trentaine de personnes prévue d’ici trois ans

Commentaires

Ajouter un commentaire